PCM用2倍オーバーサンプリングデジタルフィルタのIP"FIR_x2"を公開しました

どもです。

8月の夏休みから4ヶ月ほどかけてやっと動作確認までできたので公開します。

サンプリング周波数選択もできたぁぁぁぁぁぁぁぁぁ

— AUDIY (@AUDIY14) November 29, 2023

データも問題無し! pic.twitter.com/Gek3xQQBYP

PCMデータを2倍オーバーサンプリングするFIRデジタルフィルタIPです。

きっかけ

AUDIYがFPGAに興味を持ったのは以下のビデオがきっかけです。

CHORDというオーディオメーカーがFPGAとフリップフロップを使用してDAコンバータを実現している、ということを知り、自分でもDAコンバータの構造を知りたく、FPGAを使用したオーディオ信号処理に興味が湧いたのでした。

大学・大学院では信号処理について勉強こそすれどその実装はソフトウェアばかりで、興味こそ持ちつつもなかなか手が出せなかったのですが偶然にも就職してハードウェア設計を行うことになりました。

「・・・コレは良い機会だ!」

ということで、オーディオ信号処理で多用されることの多いオーバーサンプリングFIRフィルタの実装に着手したのでした。

参考資料

実際にオーバーサンプリングデジタルフィルタを実装するにあたり、参考とした資料はリンク先のPDFです。

https://shop.cqpub.co.jp/hanbai/books/I/I000139/I000139kou.pdf

トランジスタ技術2014年12月号~2015年1月号にかけて特集された記事の一部のようです。

PDF上の図では「RAM、ROM、乗算器、加算器1つずつでできる」とありますが、実際にそれっぽく動くようになるまでには複数のハードルがありましたので、Verilogコードのリンク先とともに共有させていただきます。

ポリフェーズ・フィルタ

乗算器、加算器を1チャンネルあたり1つしか使わないということであれば、自ずとポリフェーズ・フィルタの実装になります。

今回はオーディオ用のマスタークロック(多くの場合で22.5792MHzとか24.576MHzの整数倍だと思います。)を使用して、サンプリング周波数の整数倍だけFIRフィルタのタップ数を格納する方式にしました。

RAMのアドレス制御

オーバーサンプリングデジタルフィルタに使用するRAMですが、

- 入力はサンプリング周波数のレートでデータを保存していく

- 出力はマスタークロックに合わせ保存したデータを呼び出していく

- 最も古いデータが保存されていた場所に最新のデータを保存していく

- 入力するアドレスと出力するアドレスが重複するのは禁止

必要があります。

つまり、入力はFIFO(シフトレジスタ)のように扱いつつも出力は任意のデータを呼び出せるようにしなければなりません。

本IPではRAMがリングバッファとなるようにRAMコントローラIPを設計し、上記仕様を実現しました。

今回リングバッファを実現する方法ですが、

- 最も古いデータのアドレスを記憶しておく

- データ出力の先頭アドレスを「最も古いデータのアドレス」から一つ進め、アドレスをインクリメントさせる

- データ書き込み先のアドレスに「最も古いデータのアドレス」を指定する。

- 「最も古いデータのアドレス」を一つインクリメントさせる

- 1に戻る

を繰り返すことで実現します。

ROMアドレスの指定方法

オーバーサンプリングの説明ではよく「データの間に0を挿入してFIRフィルタを畳み込む」と説明がなされるかと思います(上記PDFにもあります)。

ただ、コレを律儀にFPGAに実装すると以下のように無駄が生じてしまいます。

- ゼロデータとFIRフィルタ係数の乗算が発生する。

- マスタークロック周波数が一定なので、1により加算できる有効データ数が減少する

ということで、今回のオーバーサンプリングデジタルフィルタではフィルタ係数を出力するためのアドレスを「奇数で一巡→偶数で一巡」と繰り返す仕様にすることで0データとの乗算が行われたことと等価の処理を実現しています。(個人的にここが最大のキモだと思います。)

ROMに格納するデータを並び替えればこんなことせずにアドレスを1ずつ増やすこともできますが、データの準備が面倒ですしね・・・・

新たなビットクロックとワードクロック

FPGAで処理する以上は最終的に外部のDAコンバータICにデータを送り出すためのビットクロックとワードクロック(サンプリング周波数のクロック)が必要です。

本IPではROMアドレスの任意ビットをそのまま出力することでコレを実現しています。

(マスタークロックの分周は危険なのでやめました)

ひょっとしたらRAMのアドレスでも同じことを実現できるかもしれませんが、ROMのほうが計算の始点・終点がハッキリしているのでこのようにしました。

積分器のリセット

デジタルフィルタでは畳み込みの実現のために積分器を使用しますが、入力データを積分し続ける一般的な積分器とは少し挙動が異なります。

FIRフィルタとデータの乗算が完了したらデータが更新されるため、FIRフィルタの係数を全て使用したら積分データをリセットする必要があります。

本IPでは先述の「新たなワードクロック」の立ち上がりエッジを検出することで「全てのFIRフィルタの係数が入力データと乗算された」として積分データをリセットすることで実現しています。

できる限りのクロックドメインクロッシングの排除

本IPは内部の処理が全てマスタークロックの立ち上がりエッジまたはたち下がりエッジに同期して動作します。

逆位相でフリップフロップを駆動する箇所があるため非同期設計が無いわけではありませんが、ビットクロックやワードクロックを一切使用していないだけでもだいぶトラブルは起こりにくい仕様になっていると思います。

I2Sで出す場合はビットクロックのたち下がりエッジに同期してデータが出力されるのが標準仕様となっています。

https://www.nxp.com/docs/en/user-manual/UM11732.pdf

かといって完全同期のためにODDRとか使い出すとベンダー依存が強くなるので考えどころではあります・・・・

ビットクロック:マスタークロックの比を1:2以上にすればODDRも必要にならないのでそれが最適解ですかね・・・

以上、実装上の工夫を今回は共有しました。

次回はRTLシミュレーションと実際にFPGAで動かす例を記したいと思います。

Analog Dicovery 3でI2Sをデコードしてみる

どもです。AUDIY( Follow @AUDIY14 )です。

今回はAnalog Discovery 3(AD3)でCombo384から出力されるI2Sをデコードし、実際に取得できるサンプルの限界を探ってみたいと思います。

Combo384について

Amanero Technnologiesが販売するUSBオーディオをI2SやDSDに変換するモジュールです。

この手のソリューションで有名なものだと他にXMOSがありますが、個人使用だとデバイスドライバが評価版だったり、モジュール形式で販売されていないこと等から個人製作だとCombo384が多用されている印象があります。

Combo384は公式ドライバをインストールするだけでサンプリング周波数384kHzまでのPCMを再生することが可能です。

今回はPCMを再生してみて各サンプリング周波数(48/96/192/384kHz)でデコードした波形を取得してみたいと思います。

ちなみにXMOSについてはInnocent Key様が過去にいろいろと検討された記事を出しています。

再生する音源

今回は以下の音源を再生したいと思います。

- サンプリング周波数:48/96/192/384kHz

- 量子化ビット数:32bit

- 収録波形:1kHz正弦波

- 再生時間:60秒

- 振幅:0dBフルスケール

Pythonを使って自身で作成した音源になります。

AD3の設定について

今回波形を取得するうえで変更しなければならない設定が複数ありましたので共有しておきたいと思います。

デフォルトのメモリ長について

2023年10月22日現在のAD3用操作ソフトウェア(Waveforms)では、立ち上げ時点でAD3のハードウェアのスペックをフルに使えるような設定がなされていません。

Device Managerでロジックアナライザのメモリの割当が最大となるように変更してあげます。

デフォルトではNo. 1が選択されていて、ロジアナ機能の1チャンネルあたり最大サンプル数が16384サンプルになっています。

No. 4(ブルーハイライト)またはNo. 5に変更することで、1チャンネルあたり最大サンプル数が32768サンプルまで拡大できます。

サンプリング周波数について

デフォルトではAnalog Discovery 2(AD2)と同じ100MHz(100MSPs/S)になっています。

Options→「Clocking」タブから、最大値の125MHzに設定してあげます。

ここまでの設定で125MSPs/S、メモリ長最大32768サンプル/chのロジアナとして使用可能になります。

I2Sデコード設定

まず、Sampleの項をFallingからRisingに変更します。

これはビットクロックのデータ取り込みエッジを指定するものです。

I2Sは規格上Fallingエッジに合わせてデータを送るため、デフォルトのままではデータの取りこぼし(メタステーブル)が発生します。

次にFormatの項ですが、多くの場合で"Two's complement"(2の補数)にしないと意図した数値が表示されないと思います。

最初"Signed"にしてて正負反転した波形が出てきてしまいました。

Showの項はデータを確認したいチャンネルを選択すればOKです。

Combo384と接続する

接続はこんな感じです(暗くてすみません・・・)

今回はロジアナのデフォルトで接続しましたが、ここはユーザーの設定で変わりますのでご注意ください。

AD3購入時に合わせてICクリップを購入しておいて正解でした。

通販コード:P-03436

いざデータ取得

48kHz

4周期ぶんほどとなりました。このときのサンプルレートは7.8125MHzです。

ビットクロックの速度が48000 Hz * 64 = 3.072MHzなので、6.2MHzまでサンプルレートを小さくしてみます。

細かくサンプルレートを微調整すれば5周期ほどまでできそうです。

ここまで見ることができれば十分かなと思います。

96kHz

細かく調整して13.889MHzのサンプルレートで取得できました。

192kHz

31.25MHzのサンプルレートで取得できました。このあたりから細かいサンプルレートの調整ができなくなってきます。

384kHz

同様に細かなサンプルレートの調整はできず、62.5MHzでやっと取得できました。

最大サンプルレートから考えると768kHzのPCMまでは確認できそうですね

384kHzを再生した状態で波形を拡大します。LチャンネルとRチャンネルで数値は一致していますし、AUDIYが確認した限りではデータの取りこぼしもなさそうです。

侮れませんねAD3。ひょっとしたらDigital Discovery程度のサンプルレート(800MSPs/S)が必要かもと思っていましたが、とうぶんは杞憂に済みそうです。

近年のオーディオDACが受けれるサンプリング周波数の多くは768kHzとか1.536MHz程度までなので。

まとめ

とりあえず、AD3のロジアナ機能でCombo384から出力されるI2S波形をデコードしてみました。

- サンプリング周波数384kHzまでは細かな調整で取得可能

- 限界はサンプリング周波数768kHzと推察される

- AD2(最大サンプルレート100MHz)はサンプリング周波数384kHzが限界な可能性がある

- AD3のハードウェアスペックをフルで活かすには細かな設定変更が必要

- I2Sデコード時は細かい設定に注意

- AUDIYの用途ではDigital Discoveryがすぐに必要になることはなさそう

これはケチらずAD3買って正解でしたわ・・・・

どんどん電子工作を加速させていきたいと思います。

バックライト付きI2Cキャラクターディスプレイの文字列表示の修正

どもです。

寒くなって暑くなってまた寒い・・・

今回は下記ブログ記事の続きです。

いちいちアドレスを指定せずとも文字列を表示できるようになりましたので、その内容を記しておきたいと思います。

アドバイスは突然に

やってきました。

先日のページで参考とさせていただいた下記ブログ記事の作者の方が読んでくださったようで、

DDRAM にデータを書くとアドレスが自動的にインクリメント/デクリメントされるはずですが,Entry Mode Set がデクリメント方向になっているために,最初の1文字目が上書きされていた,ということはないでしょうか? pic.twitter.com/gleV5MUSo2

— Lawn (@lawn_rep) October 8, 2023

確かに、AUDIYが書いたディスプレイの初期化関数ではEntry Mode SetをDecrement方向にしていました。

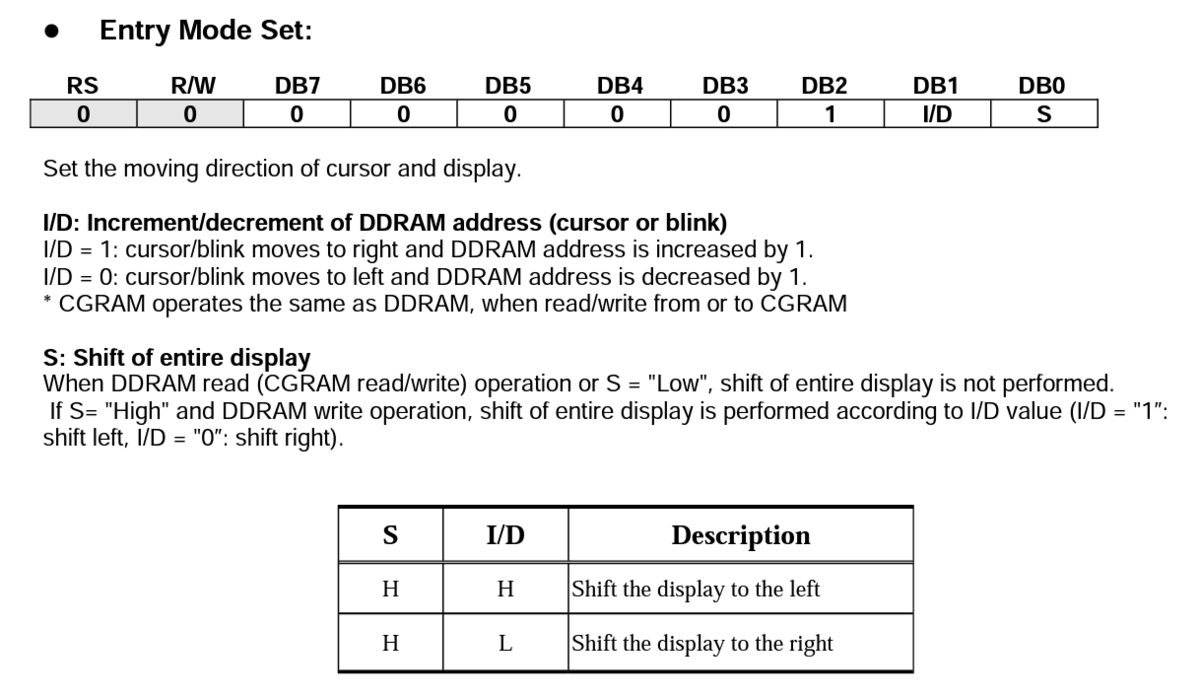

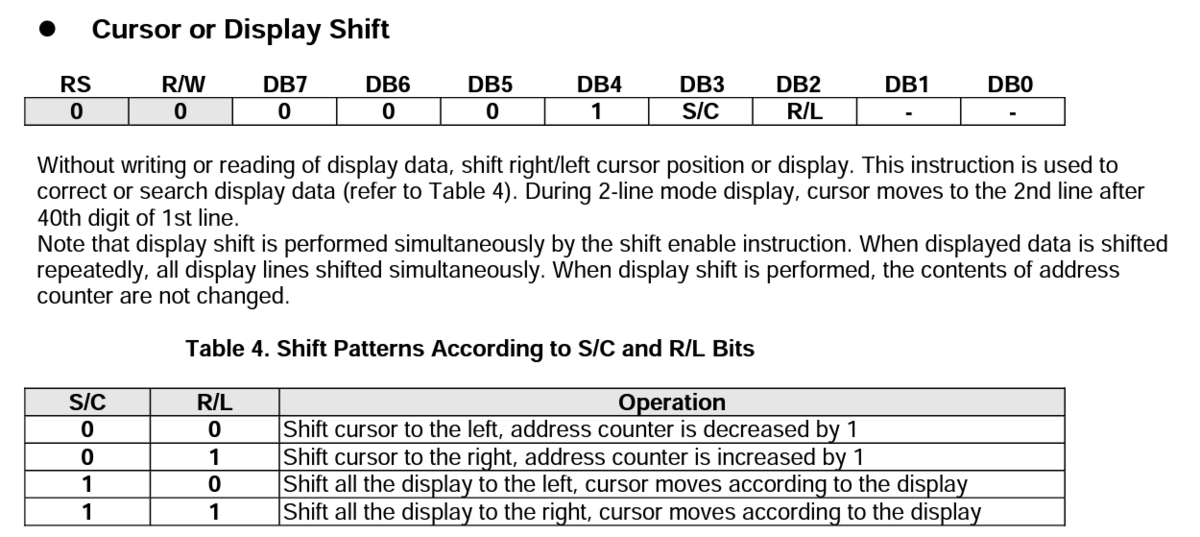

正直、このEntry Mode Setの項ですが、I/DビットとSビットの組み合わせの動作がいまいち理解できていませんでした。

もういちど制御IC(RW1063-0A)のデータシートを読んでみます。

このI/Dのビットが1のとき、自動でDDRAMのアドレスを増やしていくのでいちいちDDRAMのアドレスを指定することなく文字列表示ができるそうです。

この「Shift of entire display」は何を意味してるんですかね・・・?

ちなみにディスプレイのシフトに関する命令はもう一箇所にもあるのでこの違いがわかっていません(試してみるしかないか)。

いざ修正

修正箇所は2箇所です。

まずはEntry Mode Setの命令項目を増やしました。

もう一箇所、ACMPrintStr( )関数のループ内でのアドレス指定を削除しました。

その代わりにループ直前でENTRY_CURSOR_SHIFT命令を追加して確実に文字列を表示できるようにしています

多分表示は少し高速化できると思います。

差分についてはGitHubを見ていただければと思います。

動作確認

ばっちりです!

修正完了! pic.twitter.com/01iJDOgvPl

— AUDIY (@AUDIY14) October 21, 2023

またいろいろ作っていきたいです。

Analog Discovery 3を導入しました

どもです。

・・・・・急に寒いやん。w

ついに導入しました。

AD3、ゲットだぜ! pic.twitter.com/F7B6KW5n7w

— AUDIY (@AUDIY14) October 4, 2023

Analog Discovery 3 (AD3)です!!!!!!!!

導入の背景

前回投稿したブログ記事でも少しお話していましたが、

FPGA内部ロジックアナライザ機能を使用してPCMデータを観測しようとすると、すぐにFPGA本体のブロックRAMを食い尽くしてしまいます。

実際に上記のブログにあるPCMの波形は、余っていたブロックRAMを使い尽くした上で取得できた波形です。

ということで、これ以上大規模なFPGAの開発・実装に対しその動作を確認するうえで、個人で使用できる現実的な価格のロジックアナライザ(ロジアナ)の導入の必要性が現実味を帯びてきました。

必要な機能・条件

実際にロジアナを導入するとして、AUDIYに必要な機能や条件は以下のとおりです。

- 個人で購入できる現実的な価格であること(基準が曖昧ではあるが・・・)

- 最低でもI2Sをデコードできること(左詰めや右詰めもできるとなお良い)

- 使用方法に関する情報がインターネット検索で入手しやすいこと

- 解析に際し現実的なメモリ長を持つこと(正直見当がつかない)

AUDIYが所有しているオシロスコープ(SIGLENT SDS1104X-E)もオプションでロジアナ機能を追加できるので当初はその購入も考えてはいたものの、I2Sデコード機能がなく今回の条件から外れます。

ひとつ上のSDS2000Xシリーズにはソフトウェアオプションで解析機能を追加できるようです。

ということで、別途ロジアナを探すことにしました。

候補

そもそも電子工作界隈でロジアナをわざわざ購入する人が少ない気がしますが、おそらく以下の機種あたりが有名かと思います。

- Digilent Analog Discovery 2 (AD2)

- Digilent Analog Discovery 3 (AD3)

- Digilent Digital Discovery

- Analog Devices ADALM2000 (M2K)

ロジアナ機能だけならDigital Discoveryで良かったのですが、以下の理由からAD3を購入することにしました。

- DVM(Digital Volt Meter:テスタより更新が高速な電圧計)、ネットワークアナライザ、インピーダンスアナライザ等の解析機能が充実している

- オシロスコープの量子化ビット数がM2Kより大きい(14bit)

- M2K、AD2より高速(125MS/s)

- AD2からメモリ長が倍になっている(16kpts→32kpts)

- (性能に目を瞑れば)この手の複合機は便利

- 個人的にDigilent製品のカラー(グリーン、常盤色)が好き

特に複合機であることの便利さについては、職場でTektronixのMSO(Mixed Signal Oscilloscope:ロジアナとオシロスコープとスペアナが一緒に、かつ同時に使えるタイプのオシロスコープ)を使った経験からも重要視しており、今後趣味で電子工作を進めていくうえでは(性能こそ大差はあれど)1台持っておくと良いという判断に至りました。

(ちなみに本家MSOは個人事業主とかでも無い限り個人で買うにはあまりにも高価です。)

いざ購入

今回は秋月電子通商で購入しました。

その他複数のECサイトを調べましたが、おそらく日本国内で買うなら2023年10月現在で秋月電子での購入が最安かと思います。

通販コード:M-18129

AD3、ゲットだぜ! pic.twitter.com/F7B6KW5n7w

— AUDIY (@AUDIY14) October 4, 2023

Digilentのこのグリーン好きなんですよね

— AUDIY (@AUDIY14) October 5, 2023

わかる人います? pic.twitter.com/8TBG1cVUU5

とあるYoutube動画では「一周り以上大きい」と紹介されていますが、AD2を使ったこともあるAUDIYにとっては二周りは大型化している印象です。

最近の円安・インフレについて・・・

近年は円安やインフレによって、本来教育用途として販売されているようなAD3、M2Kもお値段が上がってしまっています。

AUDIYは社会人になってからこの世界に入りましたが、学生からこの世界に入った人にとってはなかなかツラい状況に感じます。(正直今回のAD3購入はAUDIYにとってもなかなか財布に痛い出費でした)

この手の製品は部品や本体がドル建てでの販売になることがほとんどでしょうから日本においては非常に仕方のない状況だと思いますが、こういった教育向け計測器を作るメーカーの存在は大変貴重なので、ぜひメーカーさんには頑張って生産・販売を続けていただきつつ、もし自分に子供が生まれてこういったものに興味が出てきたら痛い出費でも買ってあげたいと思う今日この頃です。

・・・・まぁそんな予定は無いんですが。w

以上、AD3購入報告でした。

次回は実際にAD3のロジアナ機能を使ってI2Sをデコードしてみたいと思います。

Efinix TRION T20開発キットとAmanero Combo384を組み合わせる(2)

どもです。

過去のこのブログですが、

すでに基板が出来上がっているのと、FPGAも動き始めたのでそろそろ積極的に記事を上げていければと思います。

接続基板のその後

その後曲線配線をしたり

うーん、エッチ!!!! pic.twitter.com/ymlhHPO2ar

— AUDIY (@AUDIY14) June 14, 2023

届いた基板を確認したら穴径を間違えていたり

だーから言わんこっちゃない(支柱の取り付け寸法ミスった pic.twitter.com/fESOdcnLt6

— AUDIY (@AUDIY14) July 18, 2023

しましたが、修正後の基板が動き始めています。

うーん、(とりあえず動いたから)ヨシっ! pic.twitter.com/4S6BsQwmKM

— AUDIY (@AUDIY14) July 29, 2023

この回路と基板設計データはGithub上に公開しています。

ライセンスもCC-BY-4.0なので、そこさえ守っていただければご自由にお使いいただければと思います。

FPGAとCombo384を繋げて何をするのか

早い話、デジタルフィルタを使用した信号処理です。

~(・ ω ・)~ヌルヌル pic.twitter.com/Ta1SaUlp62

— AUDIY (@AUDIY14) August 17, 2023

デジタルフィルタについては下記Webサイトがそこそこ詳しく、かつ難しい話はいい塩梅で割愛されてて概要をつかみやすいと思います

デジタルオーディオにおけるサンプリング周波数変換(アップサンプリング、ダウンサンプリング)、DSD→PCM変換、アンチエイリアス等、「信号処理」と呼ばれるもののほとんどはデジタルフィルタで実現されています。

それをFPGAに実装してしまおう、そういうお話です。

まずはFIRフィルタ

X (旧Twitter)ではオーバーサンプリングFIRフィルタの実装の模様を過去に投稿しています。

リングバッファ動いたよ pic.twitter.com/yS1akXMFXP

— AUDIY (@AUDIY14) August 5, 2023

あっ・・・・・・(虚無)

— AUDIY (@AUDIY14) August 17, 2023

フィルタのピークの乗算が行われる前にその両端の乗算が終わってて計算順序あべこべになっとる pic.twitter.com/FoWCtl2Nuq

あぁぁぁぁぁぁぁ行ったぁぁぁぁぁぁぁぁぁぁぁぁ!!!!!!!!!!!!!!!!!!!! pic.twitter.com/dmLrfl2d5X

— AUDIY (@AUDIY14) August 17, 2023

数年前にビヘイビアモデル(シミュレーションでのみ実行可能なモデル)をVerilogで書いたことはありましたが、FPGAに配置配線可能なRTLは初めて実装しました。

今後は何かしらの形でこのFIRフィルタを実現するRTLも解説できればと考えています(せっかくなので同人誌チャレンジしたい)。

ということで進捗報告でした。

ちなみにですが、44.1kHz→88.2kHzは動き始めています。

44.1k/48kHz→88.2k/96kHzのフィルタのコンパイル通った。

— AUDIY (@AUDIY14) September 24, 2023

意外とリソース食わない。 pic.twitter.com/x2jtZx0IHu

うぉぉぉぉぉぉぉぉぉぉぉぉぉぉ!!!!!!!!!! pic.twitter.com/Herl85z3lP

— AUDIY (@AUDIY14) September 24, 2023

Efinix Trionで実装したばかりなので、他のFPGA(例:Intel MAX10、Tang Primer 20K等)にも随時実装・検証していきたいと思います。

FPGAのロジアナ機能でPCMを読むとすぐにメモリが埋まってしまうので、ロジアナが欲しくなってきました・・・・

バックライト付きI2CキャラクターディスプレイをSTM32で操る

ご無沙汰してます。

今回ですが、STM32とバックライト付きI2C制御キャラクターディスプレイ「ACM0802C-NLW-BBW-IIC」を組み合わせて様々な文字列をディスプレイに表示させてみたので、その過程を書いていきたいと思います。

やってて色々とハマりました。

ACM0802C-NLW-BBW-IICについて

秋月電子通商で販売されている、バックライト付きの8文字x2列キャラクターディスプレイ(I2C制御タイプ)です。

通販コード:P-13519

だいたいこの手のディスプレイって本来のインターフェースは8bitパラレルだったり4bitパラレルだったりするのですが、接続線が多いと煩わしいので、ディスプレイの更新速度ではやや不利になるものの今回はI2C制御タイプにしました。

最初から怪しい匂いが・・・

このディスプレイですが、データシート上にI2C通信に関する詳細な記述がありません。

秋月の商品ページには「データシートの8ページに記載がある」旨問い合わせに回答されていますが、本当に手順しか記載がなく命令レジスタ等の記載は皆無です。

上記データシートを見ていると、4ページ目に「Contoroller IC: RW1063-0A or compatible」と記載があります。

つまり「RW1063-0A」なるディスプレイ制御ICのデータシートを入手する必要がありそうです。

RW1063-0Aデータシート入手

「これはどうしたものかなー」と思いつつRW1063-0AというICのデータシートを探していたら、同じく秋月電子通商販売の「ACM2004D-FLW-FBW-IIC」というI2C制御キャラクターディスプレイのページにRW1063-0Aのデータシートと思しきものが添付されていました。

通販コード:P-17381

これをもとに他のWebサイトでの実装例なんかも見つつ実際に文字列を表示させていきたいと思います。

追伸、「ACM2004D-FLW-FBW-IIC」のページにはArduinoのサンプルスケッチを入手することもできます。一度に表示できる文字数もACM2004D-FLW-FBW-IICのほうが多いですからこれからディスプレイを使いたい人はこちらから始めるほうが難易度は低いかもしれません。

デバイスアドレスについて

ACM0802C-NLW-BBW-IICですが、コネクタの4番、5番ピンをプルアップまたはプルダウンすることでアドレスを4通りに設定できます。(ACM0802C-NLW-BBW-IICデータシート6ページに記載)

上図のSA0、SA1がそのアドレスに相当します。つまりデバイスアドレスは16進数(2進数)で

- 0x78 (0b01111000):SA1 = 0, SA0 = 0

- 0x7A (0b01111010):SA1 = 0, SA0 = 1

- 0x7C (0b01111100):SA1 = 1, SA0 = 0

- 0x7E (0b01111110):SA1 = 1, SA0 = 1

の4通りです。

レジスタアドレス

デバイスアドレスの後に送るレジスタアドレスは2通りです(RW1063-0Aデータシート28ページに詳細記載)。

- 0x00 (0b00000000):ディスプレイに何かしらの設定を送るとき

- 0x40 (0b01000000):ディスプレイの特定箇所の文字を設定するとき

RW1063-0Aデータシート中の"Control byte"中にあるA0ビットの違いで設定します。

設定データ

設定データについてはRW1063-0Aデータシート17ページに記載があります。

ここに記載された値をレジスタアドレス0x00の後に送ることでディスプレイのオンオフや表示の消去などができます。

I2Cで制御する場合はRSやRWビットは無視します。(つまり、「Read Busy Flag and Address」の命令はI2C制御時はできません。)

AUDIYはこの命令のうち「Set DDRAM Address」にハマりました。後ほど説明します。

文字データ

一般的な半角文字はRW1063-0A内部のROMに格納されていて、少なくともカタカナ以外はレジスタアドレス0x40のあとに対応するASCIIコードを送るだけでその文字が表示されます。

例えば、小文字のaを表示させたい場合は0x40のあとに0x61(10進数97)を送ればよいです。

ふむふむ pic.twitter.com/eOE0gto723

— AUDIY (@AUDIY14) September 10, 2023

プログラミングでうまいことやれば文字列をそのまま表示できそうです。

初期化

起動後のデバイスの初期化ですが、RW1063-0Aデータシートの32ページに手順が記載されています。

待ち時間まで指定されていますね・・・

文字列の表示について

実際にSTM32マイコンでI2C制御ディスプレイを動かすブログ記事があったので参考にしましたが、制御ICが違うためか見事にハマりました。

を繰り返せば文字列が表示できるようなコードに見えますが、実際にやってみても冒頭の1文字しか表示されません。

改めてRW1063-0Aのデータシートを読んでいくと、文字列表示にとても重要なことが12~14ページに記載されていました。

詳しくはデータシートを読んでいただくとして、ざっくり言うと「文字を表示したい場所をDDRAM Addressで指定しなさい」ということです。

今回使用するACM0802C-NLW-BBW-IICは8文字、2列のディスプレイなので、初期化終了時点で1列目のアドレスは0x00 ~ 0x07、2列目のアドレスは0x40 ~ 0x47とのことです。

このアドレスの変更をRW1063-0Aデータシート17ページに記載の「Set DDRAM Address」で行うということです。

つまり順序を書くと

の2つを繰り返すことで文字列表示が実現できます。

実現した動画は以下のとおりです。

やっと文字列表示できたー pic.twitter.com/Wdl9nEPqVA

— AUDIY (@AUDIY14) September 16, 2023

ライブラリ関数の実装

いくつかのI2Cの送信について関数を作ったので解説します。

といっても設定や文字列表示に関する関数は3つです。

設定書き込み関数ACMWriteInstruction()

レジスタアドレス0x00に対し代入されたデータを送信します。

文字書き込み関数ACMPrintChar()

現在指定されているDDRAMアドレスに対し文字*strを書き込みます

やっていることはACMWriteInstruction()関数とほぼ変わりません。

※DDRAM Addressの更新は行いませんので注意してください。

文字列書き込み関数ACMPrintStr()

ディスプレイに対し入力引数LNで指定した行に文字列*strを入力します。

関数内部で行指定、文字数計算およびその文字数だけACMPrintChar()関数の繰り返しを行います。

その他にもディスプレイの初期化関数や、ディスプレイに設定されたI2Cデバイスアドレスを検索する関数を実装しています。

動かしてみる

上記リンク先の関数を組み合わせて文字列を流すプログラムを実装してみました。

ウェェェェェェイ!!!!!!!!!! pic.twitter.com/mPr1F48GGJ

— AUDIY (@AUDIY14) September 17, 2023

流れとしては

- CheckACMDeviceAddress()関数でI2Cデバイスアドレスの取得

- InitACM()関数でRW1063-0Aの初期化

- ACMPrintStr();で文字列を書き込み

- ディスプレイの表示を開始

- 1秒ごとに文字列を左にシフト

- 文字列全てをシフトし終えたら最初の状態で表示し直す

- 5と6を繰り返す

という手順です。

まとめ

ということで秋月電子通商で販売されているACM0802C-NLW-BBW-IICを使って文字列を表示させてみました。

まとめとしては

- データシートの情報が不足している

- DDRAMのアドレスの更新が文字列表示のカギ

- ACM2004D-FLW-FBW-IICから始めるほうがオススメ

です。

今回作成したドライバ(HAL使用)はGitHubにアップロードしています。

MITライセンス(2条項BSDライセンス)で公開していますのでご自由にお使いいただければと思います。

また何か進捗があればブログを更新したいと思います。

電気設計として新卒入社3年経ったので感想でも

ご無沙汰しております。

前回記事のAmanero Combo384接続基板ですが、

この界隈恒例の「寝かせる」という儀式の結果、

うーん、エッチ!!!! pic.twitter.com/ymlhHPO2ar

— AUDIY (@AUDIY14) June 14, 2023

だいぶ様変わりしました。この模様はまた後日ここに記したいと思います。

さて、今回は、

「電気設計新入社員として入社して3年の所感」を書くとしたら興味ありますか?

— AUDIY (@AUDIY14) June 16, 2023

思いの外反響が大きかったため書いてみたいと思います。

入社直後にわかる「深刻な状況」

実はAUDIY、電気設計として現在の職場に新卒入社してからちょうど3年を迎えたのですが、入社時に目の前に広がるのは異様な光景でした。

弊社は同じオフィス内にハードウェア(回路&機構)設計部署とソフトウェア設計部署が存在しますが、明らかに回路設計部署の平均年齢が高いことにひと目見て気づきます。

おそらく平均が40代後半から50代前半程度ではないでしょうか。ソフトウェア設計と比較して10歳ほど平均年齢は上になるかと思います。

そしていざ話を聞いてみるとAUDIYが入社した頃は「新卒採用を積極的に再開し始めてから3年」とのことでしたし、更には「新入社員より定年退職者が多くハードウェア設計の人数は減るばかり」という状況でした。

最近話題の「配属ガチャ失敗」とは思いませんでした(後述します)が、「とんでもない会社に来たな」と思ったのが入社直後の印象でした。

恐ろしく高いハードル

そんな回路設計部署に配属されたAUDIYですが、大学や大学院ではソフトウェア専攻だったのもあり、待ち構えていたのは「恐ろしく高いハードル」です。

弊社、現場での技術的な研修は基本的に設定されておらず、いわゆる「OJT」なのですが、「ESR」「カスコード」「位相補償」「負帰還」とかさっぱりわからないままOJTなので作る回路が「ゴミ」なのです。今でもゴミです。

そして更には業務時間中は先輩が各々の業務で忙しく、AUDIYは放置プレイで雑用を依頼されるという状況です。まぁ「雑用を依頼される」というのは新入社員全てにとってそうだとは思いますが、業務時間中に放置を喰らうと言うのはさすがに危機感を覚えました。(無論ですが、ボーッとはしてたわけではなく電気回路・電子回路を座学で勉強し直してましたよ。)

どこもそうだとは言いませんが、「OJT」を謳うハードウェア設計は裏返して言えば「設計技術を教える余裕すらないのをOJTという名目で誤魔化している」可能性があるということは今後回路設計を目指す学生は把握しておいても良いかもしれません。

こんな状況にしてしまうのなら理系で一括に採用せず専攻分野ごとに絞ればよいのにとは思います。(別分野で食わせてもらってる身で言うのもなんですが今でも思ってます。)

「配属ガチャ失敗」ではないのが最大の救い

ただこの場で伝えておきたいのは「就職先に失敗したな」とか「配属ガチャ失敗だったな」とは思っていないと言うことです。

弊社、上記でも少し書いた通り、理系はいわゆる「総合職採用」(回路・ソフト専攻関係なく「設計」として入社します)なんですが入社前にやりたいことを聞かれて、配属部署についてはある程度その意向を汲み取ってくれます(確約ではないです)。

AUDIYはそこで「FPGAやりたい!」と伝えまして、その結果FPGAもやってるハードウェア設計部署への配属になったというのが現状です。

お恥ずかしい話、それまでFPGAはソフトウェア部署で設計しているものだとばかり思ってました。ここは率直に私の企業研究不足の結果です。

そして希望通り(私にとってハードルの高い回路設計をしながらではありますが)FPGAを用いた設計を色々できていますし、これができていることが業務を続ける最大のモチベーションにもなっています。

入社2年目にして炎上案件

話がだいぶそれましたが2年目に差し掛かる少し前から設計に本格的に携わるようになります。

そしてこれが後の「炎上案件」になるなんて、当時の自分はまだ知る由もありませんでした。

しかしその傾向はすぐに分かるようになります。

まず、「大量の部品が入らない」。

これは当時コロナ禍による半導体不足もあったので、どの案件の設計をするにしても巻き込まれていたと思います。

ここまではまだ良いとして

- 電源レギュレータの納期が遅延している。担当案件で置き換えてほしい。

- FPGAが入らない。担当案件で置き換えてほしい。

- その他特定用途ICが入らない。担当案件で置き換えてほしい。

- 汎用ロジックICが入らない。担当案件で置き換えてほしい。

と、置き換えを繰り返した結果設計が遅れに遅れます。

さすがに変だと思い率直に上司に「なんかやけにうちの担当だけ置き換え依頼多くないですか?」と聞いたら衝撃の回答でした。

「マーケティング側における担当案件の優先度が低くて半導体不足のしわ寄せが集中している(≒置き換えた分を優先度の高い他の案件に回している)」

・・・・・(・・;)

いくら経営判断とはいえ「続ける必要あるのか」「優先度低いなら供給の回復を待って設計再開でも良いのでは」とは正直思ってしまいました。

さらに闇深い3年目

まぁそんな中設計を続けていくわけですが、更に炎上に追い打ちを掛けてきます。

- 一緒に回路設計担当していた延長雇用の先輩が契約更改せずに退職

- 機構設計の先輩が別部署異動(最初から関わってる設計担当が私だけになる)

- AUDIYが新入社員担当になる

・・・・・いやいやどうやれと???????????

そりゃこの記事冒頭でも書いた通り「新入社員に教えている暇は無い」のも頷けます。

私が入社した当時のように新入社員の後輩にも回路設計の軽い演習くらいはしてあげたかったんですが、そこまで回せなかったことを大変申し訳なく思っています。

そんな中で(残業時間の多さをを詰められつつも)なんとか炎上案件の設計を終えたわけですが、そこで上司から言われた言葉が

「今になって正しい設計ができていなくて残念です。」

一発目の設計でそこまで求めるなら新卒採用なんてせずに中途をバンバン雇ったらどうですかね・・・・・

このときが業務に対するモチベーションは消えましたし、転職を考え始めたきっかけでもあります。

4年目となった今

なんと、上の心ない発言をした上司と一緒に次の案件の設計をしています。

上司が求める「正しい設計」とは何なのか、しっかりと教えていただこうではありませんか!!!!!!!

ここですぐ辞めたら自分にとっても癪ですしね。

と同時に、炎上案件でできなかったことも盛り込んでより良い回路に仕上げていきたいです。(あまり大きな声では言えませんが炎上案件の最終形態はハリボテ同然となってしまいましたので・・・・)

転職どうすんの?

転職そのものについては現在も考えています。

ただ、私のように入社3年とかそこらだと中途採用というより第二新卒(もしくはそれに近い状態)での採用の市場が広いらしく、

- 未経験歓迎

- アウトソーシング

- SES(客先常駐)

関係からボコボコスカウトが来ている状況です。

正直転職サイトで調べるより自らもう少し企業や分野を絞ってその企業の中途採用に応募したほうが安全な気がしていますね。ここは調査を継続する必要があると考えています。

総括

とまぁここまでの経験から過去の自分に言いたいこと(≒異分野から回路設計新卒採用を受ける人もしくは配属される人に伝えておきたいこと)を書いておきますと

- 専攻をそのまま職業にしたいなら「理系総合職採用」は調査を念入りにしておいたほうが良い

- 未経験から回路設計に配属できる企業には相応の理由があるという認識を持っておいたほうが良い

- 職務経歴書や履歴書の随時改訂等の転職準備は少しでも可能性があるなら進めておいたほうが良い

- 転職は分野が絞れているなら転職サイト使うより企業のキャリア採用を使ったほうが良い(ここは「気がする」レベルです)

- 上記4つに加えやりたいことすらさせてくれない(配属ガチャ失敗)ならすぐに転職に動いたほうが良い(間違いなく自分より神経すり減らすと思います。)

という感じです。

なんかほとんど現職の愚痴っぽくなってしまいましたが、新規デバイスの立ち上げ含めFPGA設計に関われているのは大変うれしいですし、最近部署の再編がありましたので今後どの程度環境が改善されるかは楽しみにしているところです。

あとソフトウェア設計や機構設計は週~月に1回集まって定期的に勉強会開いてるんですが、回路設計はできていないのでそのあたりもやってみたいですね。(私みたいなゴミ回路生成機が教えてもなんなので私は受講する側で。w)

以上です。

また社会人経験5年を迎えた頃に改めて書ければと思います。