どもです。

これから暖かくなるので、

Verilator(冷やし中華)、はじめました。w

なんかVerilateするオプションをコネコネ試行錯誤してたら出力されました・・・・

— AUDIY (@AUDIY14) February 18, 2024

しまった出力されなかったときのコマンド履歴残してないです・・・ pic.twitter.com/GGDCODdsoa

Verilatorとは

Veripoolが開発するオープンソースのVerilog/SystemVerilogシミュレータです。

テストベンチやモジュールをマルチスレッド(!)のC++コードに変換(公式ではこの変換を"Verilate"と呼んでいます)し、C++コンパイラで実行可能形式にコンパイル後、実行することで高速なシミュレーションを実現しているのがウリのようです。

名だたる半導体メーカー(WD、Intel、NXPなど)でも使用されており、Chips AllianceやLinux Foundationから支援を受けているなど、業界ではかなり有名な様子。

公式では「Synopsys(VCS)/Siemens(Questa/ModelSim)/Cadence(Xcelium/Incisive/NC-Sim)と合わせた4大シミュレータの一つ」と豪語しています(本当か?)

AUDIY自身、Verilatorの勉強会を数年前に受けたことがあり、個人的には興味を持っていましたが当時はC++での記述が大量に出てきて正直「これならシミュレーションはIcarus VerilogとかQuartus等に付属しているやつで良いかな」という印象でした。

導入方法

主に3通りの導入方法があります。

- Linuxディストリビューションのパッケージマネージャを使用する

- gitからソースコードを入手しビルドする

- Dockerを使用する

それぞれの導入方法でのメリット・デメリットは以下の通りとなります。

パッケージマネージャを使用する

メリット

- 確実に安定版が導入できる

- 依存関係も合わせてインストールしてくれる

デメリット

- 各ディストリビューションでの安定版なので最新版は遅くなりがち

(機能追加やバグ修正等の対応が遅い)

gitからソースコードを入手しビルドする

メリット

- 常に最新版を導入できる

- パッケージマネージャで自動的にバージョンアップされないので特定のバージョンを長く使用可能

デメリット

- 依存関係を自分で調べて導入しておく必要がある

- OSや依存関係とのバージョンの整合性が取れないときにインストールに失敗する場合がある

- 最新版導入のたびにビルドの必要がある

Dockerを使用する

メリット

- ビルドせずに最新版を導入可能

- 常に最新版を導入できる

- コンテナを利用しているので依存関係を気にしなくて良い

デメリット

- Dockerの知識が必要

- Verilatorでは自前の環境より動作に若干時間がかかる

- VerilatorではVSCodeとの連携が困難

今回はVSCodeのプラグインと連携させてLinter機能を使いたかったのと、AUDIYが使っているUbuntu 22.04 LTSではパッケージマネージャで配布されてるVerilatorのバージョンが4と古いので、gitからソースコードを入手しビルドしたいと思います。

ビルド方法

今回はWindowsマシン上にWSL2 + Ubuntu 22.04を構築して導入したいと思います。

WSL2の導入はこの記事が詳しいと思います。

Ubuntuが導入できたらあとは以下のページの内容の通りに依存関係を導入してインストールすれば問題ないと思います。

Ubuntu 22.04の場合では「zlibcが無い」とエラーが出ますが、その場合は無視して良いです。

ちなみにですが、

Verilator 5だとC++でテストベンチを書く必要性が薄いです.

— Susumu Yamazaki (ZACKY) (@zacky1972) February 22, 2024

それ以前はC++でテストベンチ書く必要があったようですね・・・・

ちなみにC++テストベンチのサンプルコードはカオスです。

動かしてみる

テストベンチから実行形式を吐き出してみます。

とりあえずでてきた警告は無視させています。

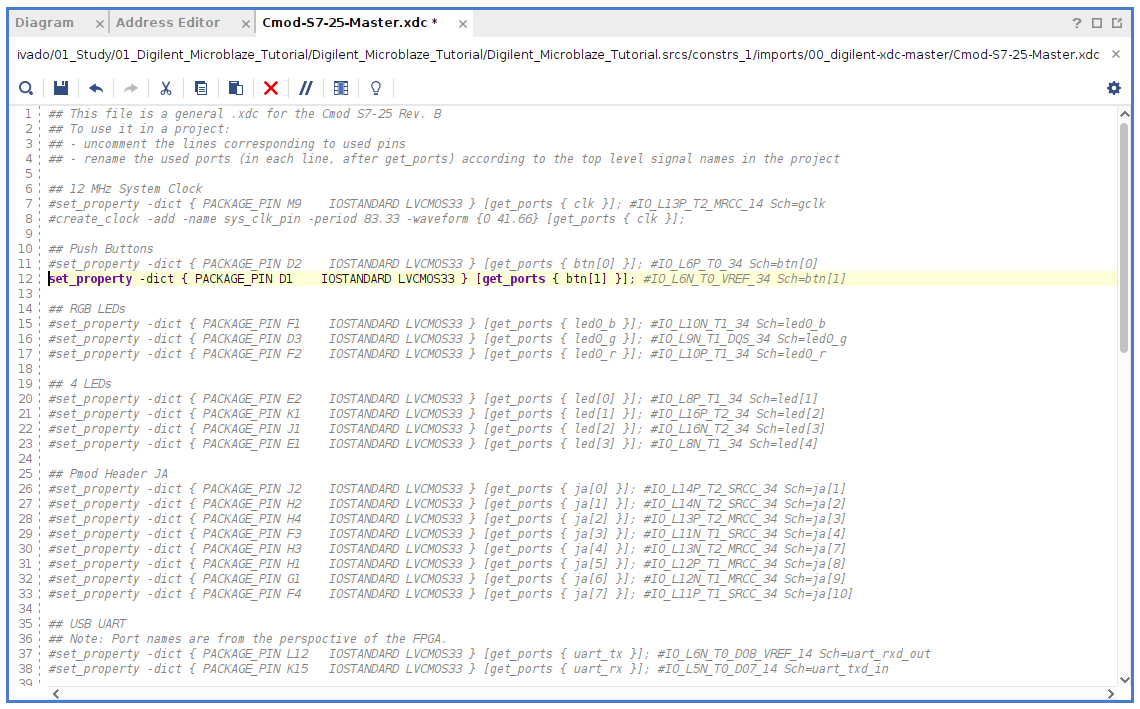

- verilator --cc --binary --timing --trace --trace-params --trace-structs --trace-underscore -Wno-TIMESCALEMOD -Wno-WIDTHTRUNC +1364-2005ext+v SDPRAM_SINGLECLK_tb.v

成功するとobj_dirというディレクトリ内に実行ファイルができますので、メモリ初期化ファイル(ram_init_file.mem)を同一ディレクトリに置いて

- ./VSDPRAM_SINGLECLK_tb

vcdファイルが作成されるので、gtkwaveで読み込めば

なんかVerilateするオプションをコネコネ試行錯誤してたら出力されました・・・・

— AUDIY (@AUDIY14) February 18, 2024

しまった出力されなかったときのコマンド履歴残してないです・・・ pic.twitter.com/GGDCODdsoa

vcd出力の際にオプションが必要になったり、一部のVerilog記述のシミュレーションが非対応だったり、

Warningが出力される時点で実行形式は生成されない(厳しいな・・・・)ので、単純なシミュレーションだけであればIcarus Verilogの方が実行オプションも少なく使いやすい印象です。

WarningやErrorは結構細かい内容が網羅されている(悪く言えば制限が強い)ので、AUDIYのような「コーディングルールがフラフラしがち」な人には良い矯正ツールだと思います。

そこで考えた

「これ、Linterとして使えないか・・・?」

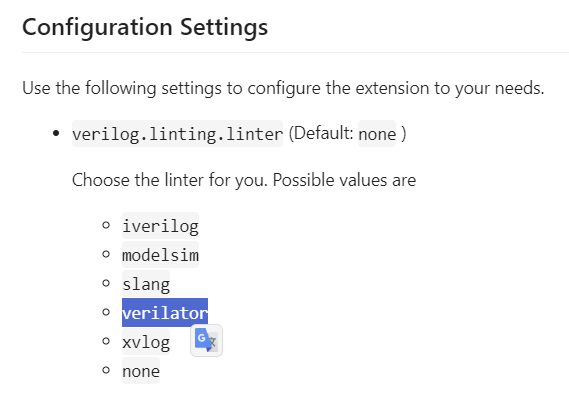

そこでAUDIYが使っているVSCodeのVerilogプラグインを調べてみると・・・・

・・・・・ありました。

Verilatorと連携してVSCode内のLinterとして使えます!

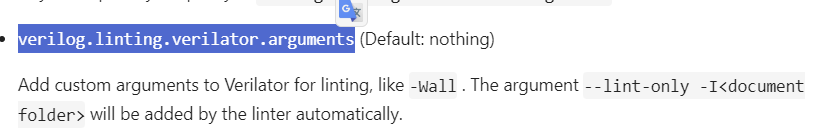

もう少し設定を追っていきますと・・・

Verilatorの実行オプションを追加できたり

WSL上に構築したVerilatorを使用することもできるようです。

それではやっていきましょう。

「Verilog > Linting: Linter」を"verilator"に設定します。

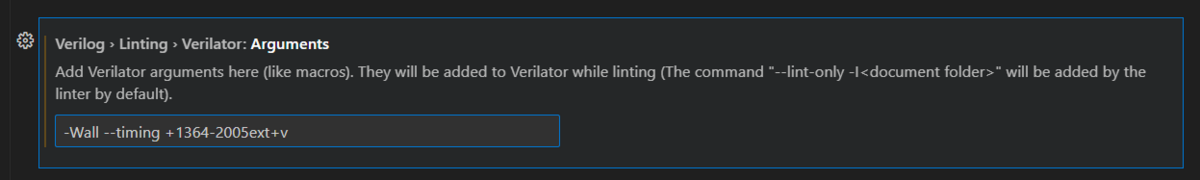

「Verilog > Linting > Verilator: Arguments」に必要なオプションを追加します。

AUDIYの場合は「警告を全て出力」「遅延評価する」「Verilog記法はVerilog-2005で指定」にしました。

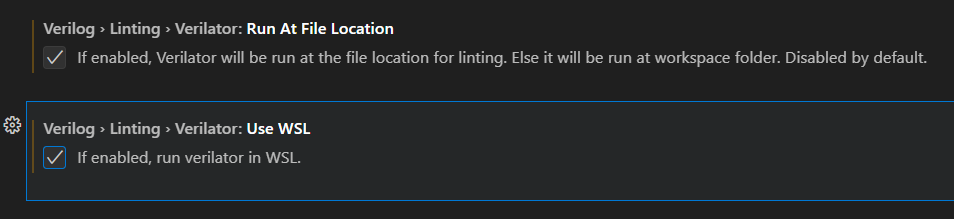

「Verilog > Linting > Verilator: Run At File Location」と「Verilog > Linting > Verilator: Use WSL」にともにチェックを付けます。

ではLinter実行結果を見ていきましょう。

Icarus VerilogとLint結果を比較

Icarus Verilog

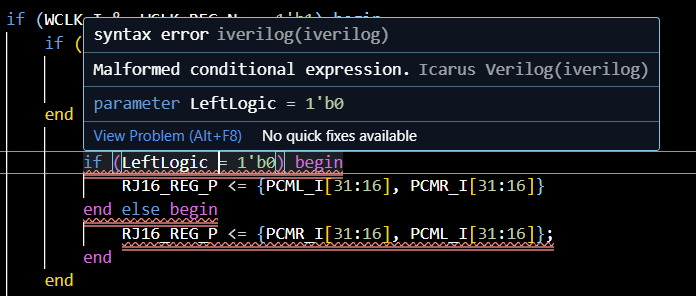

なるほどなるほど・・・

"syntax error"を教えてくれるのは良いんですが何がどうダメなのか・・・

この行は問題ないのにその前の行のエラーに引っ張られてエラーになってしまっています・・・

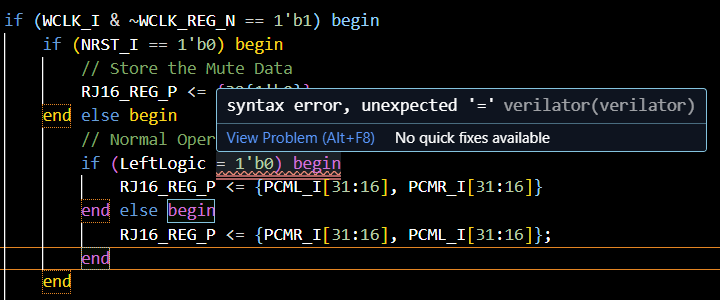

Verilator

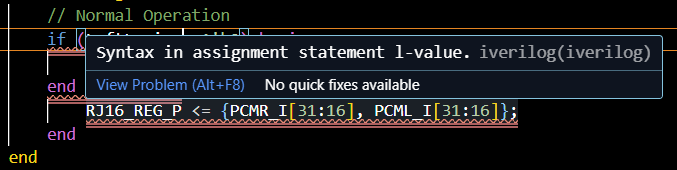

「"="がおかしくない?」とエラー箇所を推測しています

ここも同様ですね。「"end"周辺がおかしい」とわかります。

Icarus VerilogのLint機能にはありませんでしたが、VerilatorだとWarningも出してくれます。

「順序回路の中でブロッキング代入使ってるけど大丈夫?」というWarningです。

「ファイル末尾は行を入れておくのが推奨ですよ」とまで。かなり丁寧ですね。

ということで、VerilatorをLinterとして導入しました。

AUDIYのXには

https://t.co/5DdYSh9scS

— いしたに (@taichi600730) February 23, 2024

へーしゃすーぱーえんじにあ謹製なので、こちらを導入すべし

とオススメもありましたが、こちらガチガチのSystemVerilogルールでLint(wire, reg宣言すらもWarningにするほどには)してて、Verilog主体のAUDIYにはまだまだ早い感じでした(設定ファイルを編集してLintルールを細かく設定できるのでいずれは使いこなしたい)。

WindowsのみならずLinuxマシンにも導入しているので、Linterのみならずシミュレータとしても使っていければと思います。