Efinix TRION T20開発キットとAmanero Combo384を組み合わせる(1)

皆様こんにちは。お久しぶりです。

突然ではありますが、なんか欲が湧いてきたのでCombo384とEfinix Trion T20F256開発キットを使ってUSB-DACを自作したいと思います。

さすがに筐体設計まではしませんので悪しからず。w

今回は・・・

Amanero Combo384とT20F256開発キットを接続する基板を設計します。

ジャンパー線でピンヘッダ同士を接続しても良いんですが、やはり「信号線とGNDパターンが並走できる」という点で通信の安定を考えて基板を作成します。

安易に4層使ってごめんなさい pic.twitter.com/44pnoJ3pnk

— AUDIY (@AUDIY14) May 20, 2023

設計に関して

FPGAを他のデバイスと接続するときに設計者が考えないといけないことは「ピン配置」です。

IOピンならどこでも良いかと言われるとそうではなく、「クロック入力専用ピン」や「制御信号入力推奨ピン」が各FPGAデバイスに設定されていて、特にクロック入力専用ピンは「そこに入力したクロックでないと内部のD-FFを駆動できない」なんてデバイスもあります。

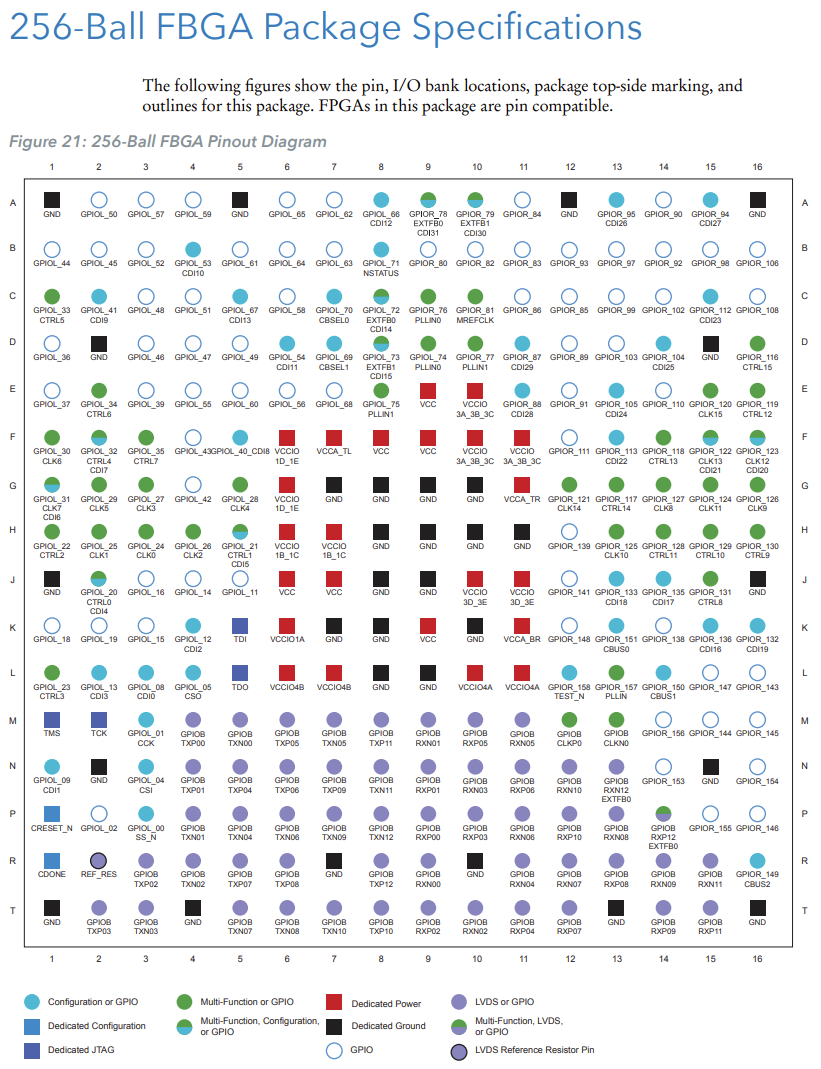

実際にTrion T20F256のピン配置を見てみます。

※「Trion Packaging User Guide v4.6」より引用

「なんのこっちゃ」と思われる方も多いと思いますが、「CLKn」(nは任意の整数)と記載のあるピン(例:G1ピンがCLK7)がクロック入力ピン、「CTRLn」が制御信号入力推奨ピン(例:H1がCTRL2)です。

それ以外にもLVDS入出力ピン(図の紫色の箇所)やPLL用クロック入力ピン(PLLINと記載のあるピン)等、配線を間違えたらとんでもありません。

開発環境でピン設定が通るか確認する

ということで、基板設計をする前に各入出力ピンの設定(クロック入力なのか、制御信号なのか、GPIOなのか)を開発環境で確認します。

流れをざっくり書きますと、

まずはトップモジュールを作成します。

内部処理が空だとエラーになるので何かしらの信号を出力にスルーアウトさせてください。

次にEfinity IDEでプロジェクトを作成し、作成したトップモジュールを論理合成します。

エラーがなければInterface Designerを起動して、トップモジュールの信号を各ピンに配置していきます。

このとき、開発キットの回路図を追いながら「どこがクロック入力か」、「どこが制御信号入力か」を探しながら配置していきます。

ピンの信号名はトップモジュールの入力・出力の信号名に合わせます。

GPIOR_120とGPIOR_124をクロック入力専用として設定したんですが、データシートを確認したらグローバルクロックラインが重複してしまっています。

2箇所重複しているので問題は無いと思います(コンパイル時に自動振り分けされるはずです)が、まぁ問題があれば基板の作り直しですかね。

※「T20 Data Sheet v5.1」より引用

スルーアウトする分には問題なさそうですので、とりあえずはコレで変換基板を発注したいと思います。

Efinix Trion T20 Development Kitで遊んでみた所感

お久しぶりです。

だいぶ前にこんな記事を書きました。

今回はその続きについて書いていきたいと思います。

Digi-keyに相談

購入したDigi-keyに相談したところ、

Digi-keyの不良品の件、自分の英語読解力が正しければ「不良品の返品は不要」と来た

— AUDIY (@AUDIY14) 2022年8月29日

いやいやいやいや大丈夫?????

ということで、

んんんんんん???

— AUDIY (@AUDIY14) 2022年9月4日

(正常動作品が届いたので2つになった) pic.twitter.com/PsjJPyQRa5

2つになってしまいました。

まぁ、勉強も兼ねて不良品はSPI/JTAGケーブルを自作して使えるようにしたいと思います。

正常動作品でいろいろ遊んでみる

正常動作品が届いたので、公式で配布されているDevelopment Kit用のTutorialを用いて一連の流れに触れてみます。

大まかな開発手順についてはVimeoに移動して動画を見てもらうこととして、今回購入した開発ボード上に色々実装してみて気づいた事等を、「EfinixのFPGA気になってるけどどうなんだろ?」と思ってる人のために少しでも気になればと思い列挙していきたいと思います。

「公式ダウンロードケーブル」が存在しない

IntelやXilinxのFPGAに触れたことのある人ならご存知かと思いますが、

各FPGAベンダーが書き込み/デバッグ用にケーブルを販売しています。

それに対しEfinixはどうかと言いますと、

https://www.efinixinc.com/docs/an006-configuring-trion-fpgas-v5.3.pdf

You can program Efinix FPGA or the SPI flash using FTDI Mini Modules.

(AN006: Configuring Trion FPGAsより引用)

とあります。

簡単に言えば「FTDIのICを使って作ってね」ということです。(ただし、市販のMini Moduleをプログラミングケーブルとして使用可)

IntelやXilinxの公式プログラミングケーブルが3万円とかするのに対しFT2232H Mini Moduleは5000円弱なので導入コストで言えば良心的ですね。

あとこの構成を採用することで「設計基板上にFTDIチップを載せてしまってユーザーがアップデートできるようにする」といったことも可能になります。

USBドライバが汎用

先述の「公式ダウンロードケーブルが存在しない」にも絡んでくるのですが、書き込みに使用するケーブルのUSBドライバが汎用ドライバ(libusb-win32)です。

また、ダウンロードにはZadigというフリーソフトウェアを使用します。

ここは開発者の考え方の違いが出てくると思いますが、量産製品に搭載する用途などではあまり好まれないのかなと思います。

ドライバのインストーラがフリーソフトウェアとなれば「開発元は今後も開発を継続できるのか」といってところに神経を使ってしまいますし、ドライバ関係周辺で問題が発生したときにベンダーがサポートしてくれるのかという点でも不安が残ります。

シミュレーション環境が貧弱

正直に言って「貧弱」と言わざるを得ません。

まず、開発環境にシミュレータが付属しません。

IntelやMicrochip、LatticeにはModelSimの機能制限版が付属したり、Xilinxは自社設計のシミュレータが付属しますが、Efinixの開発環境にはそれらがありません。

公式チュートリアルではALDEC Active-HDLで波形を確認している例がざっくり紹介されていましたが、

開発環境のドキュメンテーションを確認したところ、

- 開発環境から呼び出して使用できるのは「Icarus Verilog」「ModelSim」「Incisive」の3種類

- 開発環境のGUIからはシミュレータの呼び出しは不可能で、コマンドを実行して呼び出す必要がある

- 開発環境からのVHDL RTLシミュレーションが不可能(VHDLのシミュレーションは別途対応シミュレータを立ち上げて実行する必要がある)

- 開発環境はデフォルトでIcarus Verilogを使用してシミュレーションを実行しようとする

など、開発にVHDLを使用するエンジニアに対しては特に優しくない仕様です。

ここは素直に改善を望みます。

RTLビューアが無い

これはAUDIYが普段Intel FPGAを使用しているからというのもありますが、論理合成結果をRTLビューアのような回路図形式で見ることができません。

つまり論理合成結果からバグを見つけることは不可能に近いです。

ここもできれば機能があると嬉しいです。

開発環境の無償アップデート期間が設定されている

開発キットさえ購入すれば開発環境のソフトウェアは無料で使用できますが、無償アップデート期間は1年間のみで、以降のダウンロードやアップデートは有償(年単位での更新)になります。

こういったところもIntelやXilinx、Latticeと比較すると少々導入難易度が高いと言わざるを得ません。(アップデートさえ気にしなければ継続使用は可能)

ただし、IntelやXilinxは開発対象のFPGAデバイスによってソフトウェアの有償・無償を区別していたりするのに対し、Efinixはその制限が無いので一長一短といったところです。

UIがシンプル

IntelのFPGA開発環境であるQuartusは開発工程や設定項目毎に細かい階層構造になっているため色々見落としやすい部分もあると感じていますが、Efinixの開発環境は至ってシンプルです。

プロジェクト設定へのアクセスも2クリックで開きます。慣れてしまえば初設定や各工程で細かい作業するにはこちらのほうが早いと思います。

他にもクロック数の制限とか

某EfのFPGAでいろいろ遊んでるけど、グローバルクロックネットワーク数を超えるクロック割当はできないというド畜生仕様らしく笑ってしまった

— AUDIY (@AUDIY14) 2022年10月22日

タイミング制約とか、色々あるにはありますが、おそらく初めてFPGAに触れる人、初めてEfinixに触れる人が直面するこれまでの開発環境との違いはこんなところだと思います。

初学者・ホビーユーザー向けか?

正直なところ、現状の開発環境では初学者向けとは言えないとAUDIYは思います。

「これから初めてFPGAに触れる!」という人は、素直にTerasicやDigilentの学習キットを購入してIntelやXilinxの勉強をしたほうが幸せになれると思います。(学習用資料も豊富に揃ってますし。)

ホビーユーザーに対しては、ソフトウェア・アップデートさえ気にしなければFPGA開発経験のある人は検討の価値があると思います。というのも、

- 自前の書き込み環境を構築できる

- コンフィグレーションROMや書き込み環境のコストを安く抑えられる

- シミュレータやRTLビューアも大抵どうにかなる(AUDIYはModelSim Intel FPGA Starter EditionやYosysを組み合わせてます)

というのがそう考える理由です。

以上、AUDIYがEfinixの開発ボードでチュートリアルファイルを使って遊んでみた所感をまとめました。

せっかく動作不良品が手に入ったことですし、GPIOの数も豊富なので多くの入出力を必要とする設計や、自前の書き込み環境(FTDI FT2232Hを使った自作基板)の設計等勉強していければと思います。

積分器、微分器から学ぶ論理設計

ども。AUDIYです。(雑)

先日、FPGAでの信号処理実装で必要になったので積分器と微分器をVerilogでコーディングしたのですが、これが色々とハマって奥が深かったので共有しておこうと思います。

足し続ければイイんでしょ?引き続ければイイんでしょ?

本題に入る前に、まずはコンピュータを用いた積分・微分(数値積分、数値微分)と解析学における積分・微分の違いを明確にしておく必要があります。

基本的には関数のx軸を一定区間ごとに区切り、区間ごとに出した長方形や台形の面積を足し合わせることで実現しています。

コンピュータで面積を出す場合など精度が要求される局面ではこの区間を細かくしたりなどの様々な工夫を施していますが、今回はオーディオ信号の積分なのでそこまでは考えないことにします。

微分は積分の逆なので、一定区間ごとの関数の数値を引いていけば基本的には実現できます。

時間信号の積分器についてはこちらがわかりやすいです。

足し続けると、引き続けると・・・・

しかし、論理回路で上記記事の積分器をそのまま実現しようとすると問題が生じます。

C言語などのプログラミング言語で整数の足し算引き算を実装されたことのある方なら心当たりがあるかもしれませんが、「オーバーフロー」という現象が発生します。

たとえば、4ビットの整数に1ずつ足していく場合を考えます。

0, 1, 2, 3, 4, ..., 12, 13, 14, 15, 0, 1, .....

16は2進数で10000なので、下4ビットの値が繰り返されることで15の次は急激に0になってしまいます。これでは積分器の意味を成しません。

実際にVerilogで「足すだけ」の積分器を書いてみましょう。

module INTEGRATOR(

CLK_I,

DATA_I,

DATA_O

);

parameter DATA_Bit_Length = 4; // Bit Length

input wire CLK_I;

input wire unsigned [DATA_Bit_Length-1:0] DATA_I;

output reg unsigned [DATA_Bit_Length-1:0] DATA_O = {DATA_Bit_Length{1'b0}};

/* wire/reg */

wire unsigned [DATA_Bit_Length-1:0] DATA_SUM;

/* RTL */

assign DATA_SUM = DATA_I + DATA_O;

always @ (negedge CLK_I) begin

// Output the data with Negative Edge

DATA_O <= DATA_SUM;

end

endmodule以下はテストベンチです。

`timescale 1 ns / 1 ps

module INTEGRATOR_tb ();

reg CLK_I = 1'b0;

reg unsigned [3:0] DATA_I = 4'h1;

wire unsigned [3:0] DATA_O;

INTEGRATOR u1(

.CLK_I(CLK_I),

.DATA_I(DATA_I),

.DATA_O(DATA_O)

);

always begin

#10 CLK_I <= ~CLK_I;

end

/* Enable this section when use Icarus Verilog (iVerilog) */

/*

initial begin

$dumpfile("INTEGRATOR.vcd");

$dumpvars(0, INTEGRATOR_tb);

#20000 $finish;

end

*/

endmodule

ModelSimでRTLシミュレーションを実行してみます。

11, 12, 13, 14, 15, 0, 1, 2, ....となっています。

見にくいので波形の表示方法を変えてみましょう。

これがオーバーフローです。

微分器でも同様の事象が起こりえます。HDLに落とし込む際はこれを防ぐような処理を追加しないといけません。

では、どうするか?

まず、オーバーフローが発生する状況を想像してみます。

例えば、符号なし4bit同士の計算だと、

4'b1111 + 4'b0001 = 5'b10000 (15 + 1 = 16)

で、下4桁がそのまま出力になるのでここでオーバーフローが発生します。

つまり、オーバーフローの発生条件は「bit幅で表現できる数値の範囲を計算結果が超過したとき」となります。

出力のビット幅を無限に確保できれば良いですがそういうわけにもいきません。

そこででてくる処理が「飽和処理」(サチュレーション、クリッピング)と呼ばれるものです。

飽和処理

飽和処理とは「数値が表現可能な最大値・最小値を超える場合は最大値、最小値を保持する」処理です。

同じく4ビット符号無しでの処理を考えます。

0, 1, 2, ....., 12, 13, 14, 15, 15, 15, 15, 15, ...........

と、積分結果が15を超える場合は15を維持します。

この「15を超える」というのが重要で、今回の積分器では結果が15を超えたことを検出せねばいけません。これは「一時的に計算結果を5ビットで保存する必要がある」ということです。

検出条件

5ビット幅の符号なし整数で「15を超えたことを検出する」ということは「数値が16以上である」ことを検出すればよいわけです。

5ビット符号なし整数で16は5'b10000となり、HDLでは「数値ビットの最上位が1」が検出条件になります。

実際に確認する

Verilogコードを以下のように書き直して再度シミュレーションします。

module INTEGRATOR(

CLK_I,

DATA_I,

DATA_O

);

parameter DATA_Bit_Length = 4; // Bit Length

input wire CLK_I;

input wire unsigned [DATA_Bit_Length-1:0] DATA_I;

output reg unsigned [DATA_Bit_Length-1:0] DATA_O = {DATA_Bit_Length{1'b0}};

/* wire/reg */

wire unsigned [DATA_Bit_Length:0] DATA_SUM;

/* RTL */

assign DATA_SUM = DATA_I + DATA_O;

always @ (negedge CLK_I) begin

if (DATA_SUM[DATA_Bit_Length] == 1'b1) begin

/* Saturation */

// Ex. 4'b1111 + 4'b0001 = 4'b1111 (5'b10000)

DATA_O <= {1'b1, {(DATA_Bit_Length-1){1'b1}}};

end else begin

/* Normal Operation */

DATA_O <= DATA_SUM[DATA_Bit_Length-1:0];

end

end

endmodule

always文の中にif文で飽和処理の判定を加えます。

テストベンチはそのままで再度ModelSimでシミュレーションします。

これにて飽和処理は追加できました。今回の例では符号なしですが、符号付きの場合は・・・・少々考えてみると面白いと思います。

あと、今回の例では最小値方向の飽和処理は記述していません。

せっかくなので・・・

積分からの出力を受け取るモジュールなどがこのオーバーフローに合わせて処理(リセットなど)できるように、積分器から飽和処理のフラグを出してあげたいところです。

そこで、OFDET_O(OverFlow DETection Output)という出力を追加し、飽和処理が実行されている間論理値1を出力します。

module INTEGRATOR(

CLK_I,

DATA_I,

DATA_O,

OFDET_O

);

parameter DATA_Bit_Length = 4; // Bit Length

input wire CLK_I;

input wire unsigned [DATA_Bit_Length-1:0] DATA_I;

output reg unsigned [DATA_Bit_Length-1:0] DATA_O = {DATA_Bit_Length{1'b0}};

output reg OFDET_O = 1'b0;

/* wire/reg */

wire unsigned [DATA_Bit_Length:0] DATA_SUM;

/* RTL */

assign DATA_SUM = DATA_I + DATA_O;

always @ (negedge CLK_I) begin

if (DATA_SUM[DATA_Bit_Length] == 1'b1) begin

/* Saturation */

// Ex. 4'b1111 + 4'b0001 = 4'b1111 (5'b10000)

DATA_O <= {1'b1, {(DATA_Bit_Length-1){1'b1}}};

OFDET_O <= 1'b1;

end else begin

/* Normal Operation */

DATA_O <= DATA_SUM[DATA_Bit_Length-1:0];

OFDET_O <= 1'b0;

end

end

endmoduleテストベンチにもOFDET_Oを追加し、確認します。

`timescale 1 ns / 1 ps

module INTEGRATOR_tb ();

reg CLK_I = 1'b0;

reg unsigned [3:0] DATA_I = 4'h1;

wire unsigned [3:0] DATA_O;

wire OFDET_O;

INTEGRATOR u1(

.CLK_I(CLK_I),

.DATA_I(DATA_I),

.DATA_O(DATA_O),

.OFDET_O(OFDET_O)

);

always begin

#10 CLK_I <= ~CLK_I;

end

/* Enable this section when use Icarus Verilog (iVerilog) */

/*

initial begin

$dumpfile("INTEGRATOR.vcd");

$dumpvars(0, INTEGRATOR_tb);

#20000 $finish;

end

*/

endmodule

最初の15(4'b1111)から次の15(4'b1111→飽和処理スタート)からOFDET_OがHになっています。

今回の積分器・微分器のVerilog記述を通じて上記のような考えることが多々あったので、今回ブログにまとめてみました。

実際に符号付きに拡張したものや微分器については下記GitHubリンク内にテストベンチとともに保存していますので、ぜひ確認していただければと思います。

また、最近は一度Verilogで記述したRTLをVHDLに書き直すことにハマっていまして、両方とも記述できる人間になりたいと思っています。

コードレビュー大歓迎です。

ではまた。

Efinix Trion T20開発ボードを購入したけど・・・・

経緯

欲しかったんです。

・・・・・GPIOだらけのFPGAボードが(゚Д゚)クワッ!

電子工作する人間たるもの、基板設計して作ってしまうのが理想なのですが、FPGA/CPLDの類は半導体不足の影響を引きずっていて個人購入は未だ難しそうです。

Efinixというメーカー

2012年創業の新興メーカーで、Xilinx(現在のAMD)も出資しているようです。

Quantumアーキテクチャという技術により、柔軟なFPGA開発を可能にしていることが強みのようです。

また、FPGAベンダーだけでなく、柔軟なプログラマブルデバイス(RAP: Reconfigurable Acceleration Platform)の供給にも力を入れているとのことです。

最近、Twitterを見るとこのEfinixのFPGAを使用される方が増えている様子で、

efinixのツールを軽く触って虚無になった。

— サンマーお™️ (@xeye_) July 17, 2022

TLにEfinixのビッグウェーブが来てる(みんながんばれ)

— 河野 (@fcr0842361) July 19, 2022

Efinixはじめました

— miyox (@miyox) July 17, 2022

まぁ、某I社も某X社もこんな供給状況じゃ他のベンダーに興味が行きますよねー・・・

調べていたら

こんなのを見つけました。

なんとGPIOだけで89ピン(!)あります!

しかもユーザーガイドを見たら、「LVDSピンもシングルエンドGPIOとして使用可能」とのことです。

AUDIYとしてはDE0-Nanoをずっと待っていましたが、

入荷される様子が一向に無いので、Efinix Trion T20で思い切って遊んでみることにします。

届いたはいいが・・・

結果から言うと、初期不良品(と思われる)を引いてしまいました。

Efinix Trion T20評価ボード届いたけど、USBドライバーが入らない.....

— AUDIY (@AUDIY14) August 20, 2022

何かとぶつかってる? pic.twitter.com/vHD4eGJOK4

何度かUSBケーブルを抜き挿しすると正しく認識されることもあるのですが、大抵の場合で下記のように接続が確立されません。

不明なUSBデバイスになるんだよな pic.twitter.com/ClnJ1vYL4S

— AUDIY (@AUDIY14) August 20, 2022

USBケーブルを変えても同様の症状だったため、ボード本体の不良と思われます。

ということで、現在購入先に初期不良で交換依頼中です。

さっそく遊びたかったですが、正常動作品の入手を待つことにします・・・

ディジタル技術検定2級(情報)を取得しました

ご無沙汰してます。

更新が滞っており大変申し訳ございません。

専門知識を少しずつ勉強した証拠を獲得していこうと、下記試験の勉強をしておりました。

今回、無事に合格し合格通知を受け取りましたので受験までの過程と今後の展望についてブログに示したいと思います。

この検定は何?

ラジオ・音響技能検定(懐かしく思われる方もいらっしゃるのでは?)の休止後にその中のコンピュータ関連分野を独立させて発足された検定のようです。

文科省後援なのである程度信頼も置ける民間資格なのではないでしょうか。

就職してから電子回路設計の門戸を叩くにあたり、電子回路設計関連の資格を取得して実務に活かすことができればと考えていました。

ですが電子回路設計に関連する資格ってそこまで多くないようで、大体揃って出てくるのが

- ディジタル技術検定

- 第一級陸上無線技師

- EMC設計技術者資格

という感じです。あと最難関だと技術士(電気電子)でしょうか。

難易度で言えばディジタル技術検定が初心者から入りやすい印象でしたので、まずはここから取得していくことにしました。

まずは情報分野から

で、過去問を一通り見てみたのですが、2級情報部門が大学で学んだ分野が総合的に出されており肩慣らしには十分な印象です。

2級制御もある程度は網羅されていたのですが、伝達関数などの制御工学は大学では講義の教員と馬が合わず未受講であったため、少し時間をかけて勉強することに。(あと当時はラプラス変換で躓いた記憶)

ちなみに、2級の各部門に求められるスキルは以下の通りです。

勉強

基本的には公式に出版されている「受験準備書」を購入して一通り出題内容をおさらいし、

あとはひたすらWebサイトで制限時間内で模擬試験形式で過去問題を解きまくり、

知識的に不足しているところを再度受験準備書やググったりして復習していきました。

重点的に勉強した部分

問題の割合としては知識を問う問題が多いのですが、「配点が非公開」となっていることや、公式に「最後のプログラミング問題の配点が大きい」と述べられていることから、以下3つの分野は重点的に勉強しました

論理回路設計

AND、OR、NOTを組み合わせた組み合わせ回路設計について問われます。筆者が解いた過去問の中ではXORや、D-FFを使用した順序回路の出題はありませんでした。

「カルノー図」ではなく「ベイチ図」が多用されており、これまでカルノー図で論理設計してきた人は少々慣れが必要です。

加法標準形、乗法標準形、それらを利用した冗長な(省略できる)論理式など、この分野は論理設計だけでなくそれらを駆使した考え方も問われました。

符号理論

巡回符号や、行列式を用いた符号の誤り訂正など基礎的な内容が問われます。

しかも項の数が6つほどあるので、持ち込みの許されている関数電卓では対応できない場合がほとんどだと思います。

行列式の計算ミスに常時気をつけておけば大丈夫かと思いますが、生成多項式や情報多項式などの用語も出てくるので復習は必要です。

C言語プログラミング

日本語で仕様を説明されたソフトウェアをC言語の穴埋め形式でコーディングしていきます。

問題テーマはバラバラですが、C言語コードそのものは基礎的な内容で、ポインタや構造体、math.hなどのライブラリを使った問題は基本的に出題されないようです。

私は解いた問題を答え合わせした後一旦コーディングして実際にPC上で実行して確かめました。おそらくそうしておくほうが「どんな間違いを犯す可能性があるか」も予想できると思います。

ディジタル技術検定終了!

— AUDIY (@AUDIY14) June 26, 2022

ホテル着いたらプログラミング問題実際にコーディングして答え合わせや!!

実際に受けた感想

私は公開会場まで移動して受験したのですが、会場がとある高専だったため

受験生が高専生ばかりで若さが眩しすぎて死にそう

— AUDIY (@AUDIY14) June 26, 2022

社会人は圧倒的に少なかったですね。高専生が同じ級を受験できていることから考えても、専門分野を勉強している高校生や大学生の時点で取得できる資格だと思います。

出題内容はこれまでの傾向と大きく変わらず、

- 論理回路設計

- 符号理論

- 知識問題

- プログラミング問題

の順番だったのですが、論理回路設計で少しパニックになってしまい冒頭で時間を使ってしまったものの、全問解くことができました。

いちおう途中退室も可能だったのですが、解答に悩んだ問題も数問出たため、私は全て解き終わった後に時間いっぱい使って解答漏れ等を確認し、試験を終了しました。

知識問題ですが、マルチメディア関係の技術に関する問題が数回に1度の割合で出てくるようです。ちょうどその回に当たったらしく、2問ほど確認していない問題がでてきて少々戸惑いました・・・・

合否通知まで

およそ1ヶ月かかりますが、自己採点は試験の1週間後あたりにできます。

筆者は40問中34問正解でした。

合格通知

無事受け取りました。

ディジタル技術検定情報2級合格しました! pic.twitter.com/U0Clbg2RfL

— AUDIY (@AUDIY14) August 1, 2022

申請すれば合格証明書の発行もできるため、学校や職場で資格を登録するのも可能です。

早速2級制御の準備書も取り寄せたため、次回は2022年11月に受験予定です。

おそらく、制御分野のほうが職場でいろいろと活かせるかもしれませんね・・・

以上、社会人になって初めての受験回顧録でした。

日本でもエンジニアに求められる技術力は段々と厳しくなってきていますから、私も勉強を続けて国家資格の一つくらいは持っておきたいですね。

特に、エンベデッドシステムスペシャリストとか興味があります。(何年後になることやら)

また年末に制御2級の受験記を書きたいと思います。

筆者の電子工作環境

ここでは筆者が電子工作やプログラミングをするにあたり使用している環境を列挙していきます。

ハードウェア

PC

Lenovo ThinkStation P340 SFF

- CPU: Intel Core i7-10700

- GPU: NVIDIA Quadro P1000

- メモリ: DDR4 32GB (8GB x 4)

- ストレージ (Cドライブ): 512GB NVMe PCIe Gen3x4 M.2 SSD

- ストレージ (Eドライブ): 1TB SATA 2.5インチ SSD

- ディスプレイ: Lenovo ThinkVision p24q-20

Lenovo ThinkPad X1 Carbon 7th

マイコンボード

STMicroelectronics NUCLEO-F411RE

STMicroelectronics NUCLEO-F446RE

FPGAボード

Terasic DE10-Lite (Intel MAX10 10M50DAF484C7G搭載版)

Efinix Trion T20 BGA256 development kit

オシロスコープ

SIGLENT SDS1104X-E

- サンプリング: 1GSa/s

- 帯域幅: 100MHz

- チャンネル数: 4チャンネル

直流安定化電源

SIGLENT SPD3303C

マルチテスター

WH5000

はんだごて

HAKKO FX-600

その他

Combo384互換ボード

ADALP2000

ソフトウェア

テキストエディタ

C/C++プログラミング環境

静的解析ツール

Cppcheck

コンパイラ

Intel oneAPI DPC++ /C++ Compiler

その他C/C++ライブラリ

Intel oneAPI Base ToolKit

Boost C++ Libraries

Pythonプログラミング環境

Anaconda3

STM32マイコン開発環境

STMicroelectronics STM32CubeIDE 1.13.0

FPGA開発環境

Intel Quartus Prime 22.1 Lite Edition

Efinix Efinity IDE v2023.1

回路シミュレーション

基板設計CAD

KiCad 6.0.11

リアルタイムDSDコンバータの出力波形をもう少し整える

ご無沙汰です。

前回出力波形を確認したリアルタイムDSDコンバータですが、

こんなに高調波が乗る理由についてはド素人なのでわからず、

- FPGAの出力がローパスフィルタの負荷を駆動できていない

- 1次ΔΣの1bit出力だとこんなもん

と予想をつけて、まずはローパスフィルタをアクティブタイプにしてみました。

DSDをIIRフィルタに通したシミュレーション。シミュレーション上では正しく正弦波が出る。

— AUDIY (@AUDIY14) February 26, 2022

FPGAの出力電圧がパッシブのローパスを駆動できていないのかもしれない・・・ pic.twitter.com/CHIrtdXZgM

やっぱりダメだったのでローパスのカットオフ周波数を思い切って20kHz→2kHzに。

— AUDIY (@AUDIY14) February 26, 2022

やっぱり奇数次高調波を取り除かないと低周波が厳しい。1bitの1次ΔΣって性能かなり出しづらいのでは・・・・ pic.twitter.com/a7xNE8EybR

変調率をもう少し下げるのと、強いバッファをいれると改善が期待できる。どんな回路にしてる?

— すぱっしゅ@元こうせんぐらし(ISE→vivado移行中) (@hajime__725) February 26, 2022

後は、フィルタのgndレベルをH/Lの中間に持っていくと上下の非対称性による奇数次高調波は低減可能

ちなみに変調率も下げるのもさることながら、元信号のアップサンプリングも同様に十分に大きくしないとダメです。数MHz級はほしい

— PentliumEE💉💉 (@7GHz) February 26, 2022

「変調率」というキーワードがそろって出てきました。

変調率という言葉自体が初耳だったのですが、「音量を下げれば変調率も下がる」とのこと。

確かにAUDIY、波形確認の際は1kHzの0dBFSを再生しておりました。

再生ソフトウェア側で音量を1.5dB下げてみると・・・・

変調率(音量)を下げてみてはという助言を頂いたので試してみた

— AUDIY (@AUDIY14) February 27, 2022

うぉぉぉぉぉなんかそれっぽくなった! pic.twitter.com/X5nXicUNCJ

確かにそれっぽくなりました!

一歩前進!

一つ気になること

ここで一つ気になることがあります。

それは「このΔΣ変調した1bit信号をモノリシックのオーディオ用DAコンバータに入力するとどうなるのか」ということです。

同じように歪むのか、はたまたキレイに再生してくれるのか気になります(DACによる気もしますが・・・・)

いつかDSD対応のモノリシックDAC基板を起こして検証してみたいものです。

今後の展望

さて、今回波形がそれっぽくなってきたわけですが、精度としては波形を見た感じ2.5bit程度でまだまだです。

なんとか第一関門は突破したので、今後は

- 精度の向上(オーバーサンプリングの実装&次数を増やす)

- 出力bit数の向上、PWM出力(もうDSDコンバータではなくなってしまう)

あたりで遊んでいきたいと思います。

ただ次数を増やすと発散の危険と隣り合わせなので、少し勉強する時間をください・・・・

3月にΔΣ変調に関する「例の専門書」を購入予定ですので。

その間にPT8211Sや、

R-2RマルチビットDACの評価ボード作ってるんだけど

— AUDIY (@AUDIY14) March 11, 2022

回路図やべぇ pic.twitter.com/u7eg45yY0I

少しずつではありますが進めていきたいと思います!